中国科学院研究生数字集成电路设计讲义 集成电路设计的核心要素与实践

数字集成电路设计是现代微电子技术的基石,中国科学院研究生阶段的数字集成电路设计讲义系统性地阐述了从理论到实践的全过程。本文将基于讲义的核心内容,概述集成电路设计的关键环节、技术挑战与发展趋势。

集成电路设计始于系统级设计,明确芯片的功能、性能指标与功耗预算。设计者需进行高层次建模与仿真,利用硬件描述语言(如Verilog或VHDL)描述电路行为,这是将抽象概念转化为可操作设计的第一步。中国科学院的研究生课程强调这一阶段的创新思维与系统优化能力,培养学生在复杂约束下进行架构探索的能力。

逻辑综合与验证是设计的核心环节。综合工具将行为级描述转换为门级网表,优化面积、时序和功耗。中国科学院讲义详细讲解了静态时序分析、形式验证与测试向量生成,确保设计在逻辑功能与时序约束上的正确性。研究生通过实验掌握EDA工具的使用,理解算法背后的物理意义,这是衔接理论与工艺的关键。

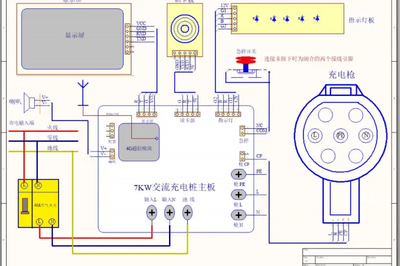

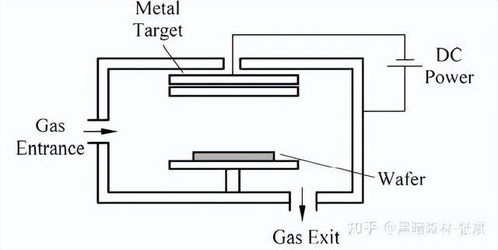

物理设计涉及布局布线,将逻辑网表映射到实际硅片。讲义涵盖版图设计、时钟树综合、电源规划等专题,突出纳米级工艺下的互连线效应、信号完整性与功耗管理。中国科学院在先进工艺节点研究方面具有深厚积累,课程结合实例分析如时序收敛、设计规则检查等实战问题,培养学生的工程实现能力。

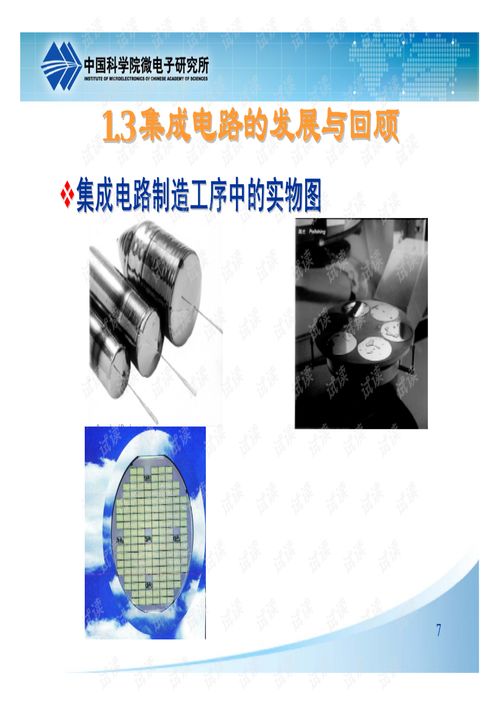

设计流程的终点是流片与测试。讲义介绍芯片制造后的测试策略、可测试性设计(DFT)与可靠性评估。中国科学院注重产学研结合,许多研究课题面向实际应用,如人工智能加速器、通信芯片等,使学生体验从设计到产品的完整链条。

集成电路设计面临摩尔定律放缓后的新挑战。中国科学院讲义前瞻性地探讨了异构集成、近似计算、开源EDA等方向,鼓励研究生探索新材料、新架构下的设计方法学。通过这门课程,学生不仅掌握技术细节,更培养解决前沿问题的创新能力,为中国集成电路产业的自主发展储备高端人才。

中国科学院研究生数字集成电路设计讲义是一套融合基础理论与工程实践的权威指南,它系统化地构建了学生的知识体系,并激发他们在这一关键领域的探索热情。

如若转载,请注明出处:http://www.iswapace.com/product/60.html

更新时间:2026-04-14 15:59:15