芯片级静电放电(ESD)保护电路设计 硬件防护与软件开发协同

在集成电路(IC)设计与制造中,静电放电(ESD)保护电路的设计至关重要。它直接关系到芯片在制造、封装、测试及最终应用中的可靠性与良率。一个完整的ESD防护体系不仅涉及精密的硬件电路设计,也离不开配套的软件开发与验证工具的支持。本文将探讨MOS芯片ESD保护电路的设计要点,并阐述软件开发在此过程中的协同作用。

一、ESD保护电路的核心设计原理

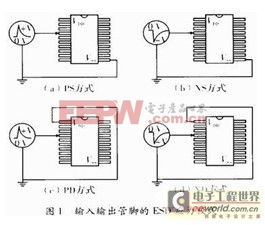

ESD保护电路的核心任务,是在芯片引脚与内部核心电路之间构建一个可控的低阻抗放电路径,在极短时间内(纳秒级)泄放高达数千伏的ESD脉冲,并将内部电路两端的电压钳位在安全水平。对于基于MOS工艺的芯片,设计需重点关注:

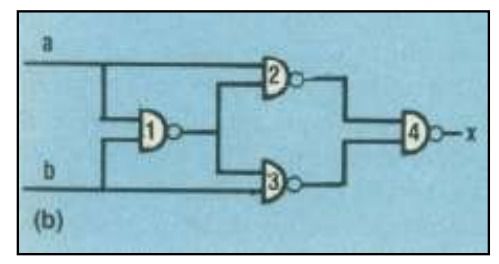

- 触发机制:设计能快速响应ESD事件的触发电路,如RC触发的MOS管、栅极接地NMOS(GGNMOS)或硅控整流器(SCR)。

- 泄放能力:确保保护器件具有足够的尺寸和结构,以承载大电流而不失效。这需要精确的布局布线(Layout),避免电流集中和热失效。

- 布局与寄生效应:保护器件必须紧邻焊盘放置,以最小化寄生电阻和电感。需仔细评估保护电路本身引入的寄生电容对高速信号完整性的影响。

- 全芯片防护网络:建立从所有输入/输出(I/O)引脚、电源轨到地的完整协同防护网络,确保ESD电流有预设的全局泄放路径。

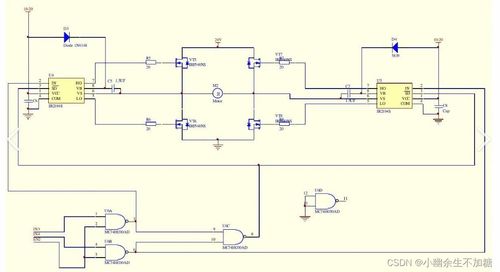

二、ESD保护的硬件设计流程与方法

典型的设计流程包括:

- 标准与目标设定:依据JEDEC、AEC-Q100等行业标准(如人体模型HBM、机器模型MM、充电器件模型CDM)设定防护等级。

- 器件选型与仿真:利用TCAD(工艺计算机辅助设计)工具仿真保护器件在ESD应力下的电热行为。使用SPICE模型进行电路级仿真,验证触发电压、维持电压和钳位特性。

- 版图实现:采用多指状(multi-finger)结构、增加接触孔、使用哑元(dummy)器件等版图技巧来提升均匀性和鲁棒性。电源钳位(Power Clamp)电路的设计与分布也是关键。

- 测试验证:通过片上测试结构和专门的ESD测试仪进行硅后验证,确保设计达标。

三、软件开发在ESD设计中的关键作用

软件开发并非直接设计保护电路,而是通过提供自动化工具、模型和流程,极大地提升设计效率和准确性:

- 设计与仿真自动化:

- EDA脚本与平台:使用Perl、Python或Tcl脚本自动生成保护单元的版图,或集成不同仿真工具的工作流。

- 模型开发:开发精确的ESD器件紧凑模型(Compact Model),供电路仿真器使用。这需要软件工程师与器件物理专家紧密合作。

- 验证与检查:

- 电气规则检查(ERC):开发定制化的ERC规则,用于检查版图中ESD路径的连通性、是否存在悬空栅极等。

- 布局与原理图对比(LVS):确保复杂的ESD保护网络版图与电路图完全一致。

- 寄生参数提取:提取保护网络及互连线的寄生电阻/电容/电感,进行更精确的仿真。

- 数据分析与良率管理:

- 测试数据分析软件:开发或使用软件分析大量ESD测试数据,快速定位失效点和薄弱环节,进行统计良率分析。

- 知识库与IP管理:建立可重用的ESD保护电路知识产权(IP)库,并通过软件进行版本管理和集成验证。

四、硬件与软件的协同优化

最先进的ESD设计是硬件与软件深度协同的结果。例如,利用机器学习的软件算法,可以分析历史测试数据和仿真结果,预测新设计的最佳保护器件尺寸和布局参数,从而减少设计迭代次数。针对特定应用(如超高频RF芯片),需要通过软件协同仿真,精细权衡ESD防护等级与信号性能(如插入损耗)。

结论

MOS芯片的ESD保护电路设计是一个多学科交叉的工程领域。强大的硬件设计是确保芯片物理坚固性的基石,而高效的软件开发则是实现设计自动化、验证严谨化和分析智能化的翅膀。二者相辅相成,共同构成了现代高可靠性芯片设计中不可或缺的防护体系。随着工艺节点不断演进和芯片复杂度提升,这种“硬软结合”的协同设计方法将变得愈加重要。

如若转载,请注明出处:http://www.iswapace.com/product/84.html

更新时间:2026-04-02 00:08:38